- 您现在的位置:买卖IC网 > Sheet目录3876 > PIC16F1526-I/PT (Microchip Technology)MCU 14KB FLASH 768B RAM 64-TQFP

PIC16(L)F1526/27

DS41458A-page 36

Preliminary

2011 Microchip Technology Inc.

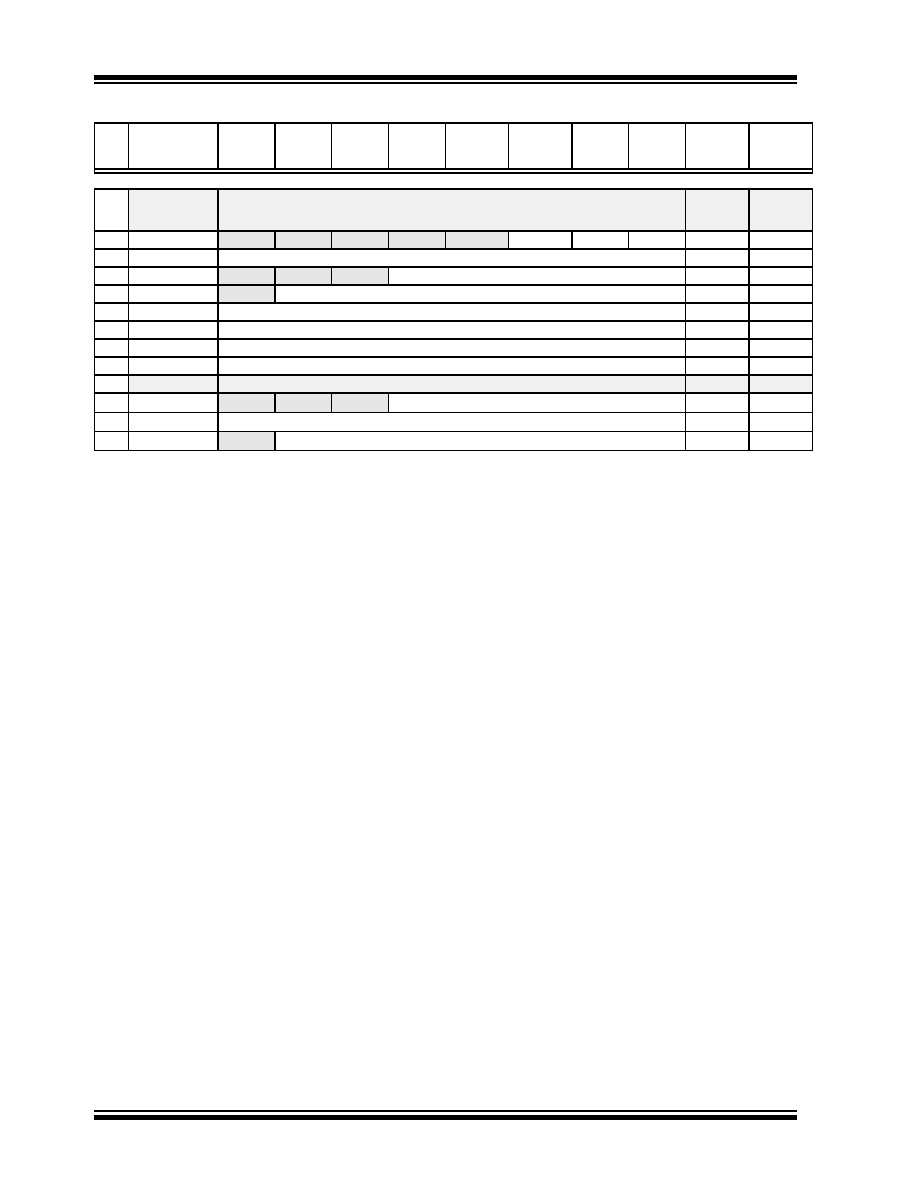

Bank 31

F8Ch

—

FE3h

—

Unimplemented

—

FE4h STATUS_SHAD

—

Z_SHAD

DC_SHAD C_SHAD ---- -xxx ---- -uuu

FE5h WREG_SHAD

Working Register Normal (Non-ICD) Shadow

xxxx xxxx uuuu uuuu

FE6h BSR_SHAD

—

Bank Select Register Normal (Non-ICD) Shadow

---x xxxx ---u uuuu

FE7h PCLATH_SHAD

—

Program Counter Latch High Register Normal (Non-ICD) Shadow

-xxx xxxx uuuu uuuu

FE8h FSR0L_SHAD

Indirect Data Memory Address 0 Low Pointer Normal (Non-ICD) Shadow

xxxx xxxx uuuu uuuu

FE9h FSR0H_SHAD

Indirect Data Memory Address 0 High Pointer Normal (Non-ICD) Shadow

xxxx xxxx uuuu uuuu

FEAh FSR1L_SHAD

Indirect Data Memory Address 1 Low Pointer Normal (Non-ICD) Shadow

xxxx xxxx uuuu uuuu

FEBh FSR1H_SHAD

Indirect Data Memory Address 1 High Pointer Normal (Non-ICD) Shadow

xxxx xxxx uuuu uuuu

FECh —

Unimplemented

—

FEDh STKPTR

—

Current Stack Pointer

---1 1111 ---1 1111

FEEh TOSL

Top of Stack Low byte

xxxx xxxx uuuu uuuu

FEFh TOSH

—

Top of Stack High byte

-xxx xxxx -uuu uuuu

TABLE 3-2:

SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Addr

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Value on

POR, BOR

Value on all

other

Resets

Legend:

x

= unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as ‘0’, r = reserved.

Shaded locations are unimplemented, read as ‘0’.

Note

1:

PIC16F1526/7 only.

2:

Unimplemented, read as ‘1’.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC24F08KL401-I/SO

IC MCU 16BIT 8KB FLASH 20-SOIC

PIC18F13K50-I/MQ

IC PIC MCU FLASH 512KX8 20-QFN

PIC16F1934-I/PT

IC PIC MCU FLASH 256KX7 44-TQFP

PIC24F16KL402-I/SS

IC MCU 16BIT 16KB FLASH 28-SSOP

PIC16LF1934-I/PT

IC PIC MCU FLASH 256KX7 44-TQFP

PIC16C58B-20/P

IC MCU OTP 2KX12 18DIP

PIC18F24K20-I/SP

IC PIC MCU FLASH 8KX16 28-DIP

PIC16F1936-I/SP

IC PIC MCU FLASH 512KX14 28SPDIP

相关代理商/技术参数

PIC16F1526-I/PT

制造商:Microchip Technology Inc 功能描述:IC 8BIT MCU PIC16F 20 MHz 64-TQFP 制造商:Microchip Technology Inc 功能描述:IC, 8BIT MCU, PIC16F, 20MHz, TQFP-64

PIC16F1526T-I/MR

功能描述:8位微控制器 -MCU 14KB FL 768B RAM 10bit ADC 1.8-5.5V

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1526T-I/PT

功能描述:8位微控制器 -MCU 14KB Flash RAM 768b nanoWatt

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1527-E/MR

功能描述:8位微控制器 -MCU 28KB FL 1536B RAM 10bit ADC 1.8-5.5V

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1527-E/PT

功能描述:8位微控制器 -MCU 14KB Flash RAM 768b nanoWatt

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1527-I/MR

功能描述:8位微控制器 -MCU 28KB FL 1536B RAM 10bit ADC 1.8-5.5V

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1527-I/MR

制造商:Microchip Technology Inc 功能描述:IC 8BIT MCU PIC16F 20 MHz 64-QFN 制造商:Microchip Technology Inc 功能描述:IC, 8BIT MCU, PIC16F, 20 MHz, 64-QFN; Controller Family/Series:PIC16F; Core Size:8bit; No. of I/O's:54; Program Memory Size:28KB; RAM Memory Size:1536Byte; CPU Speed:20MHz; Oscillator Type:External, Internal; No. of Timers:9 ;RoHS Compliant: No

PIC16F1527-I/PT

功能描述:8位微控制器 -MCU 14KB Flash RAM 768b nanoWatt

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT